July 11, 2024

TT04 - looking inside TinyTapeout 4 (GDS included) : weekend die-shot

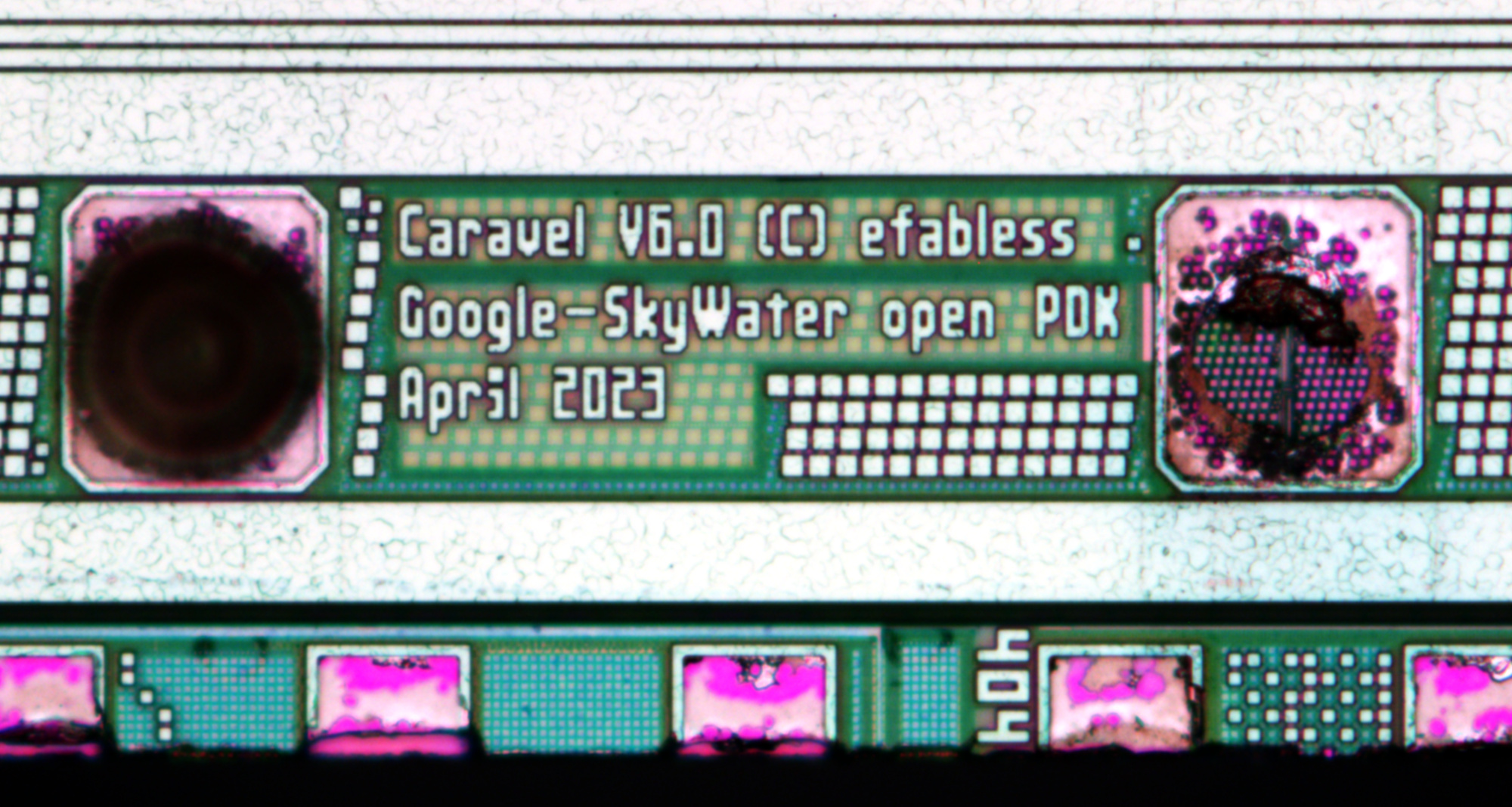

Through TinyTapeout project (TT04) I got to design a microchip with a bunch of oscillators, had it working in my hands and inspected under microscope. Now we'll be able to verify if manufactured chip matches GDS design files and is there any secret sauce!Feel free to inspect source design using KLayout, SKY130 layer definitions, and finally full original GDS design. You can hide metals and DECAP cells in KLayout to make it easier to look around and compare to photos.

You can also watch video interview with decapsulation process here.

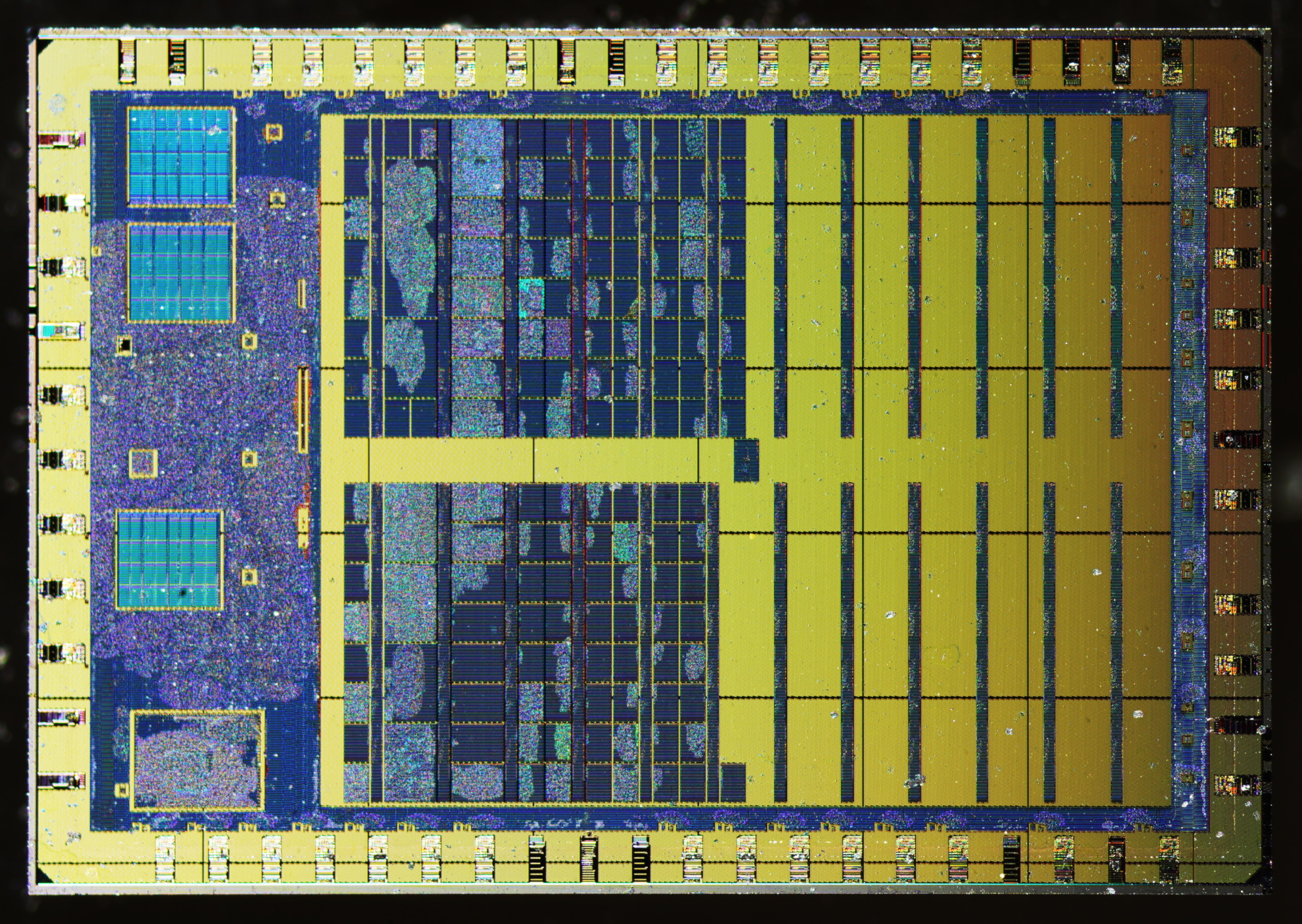

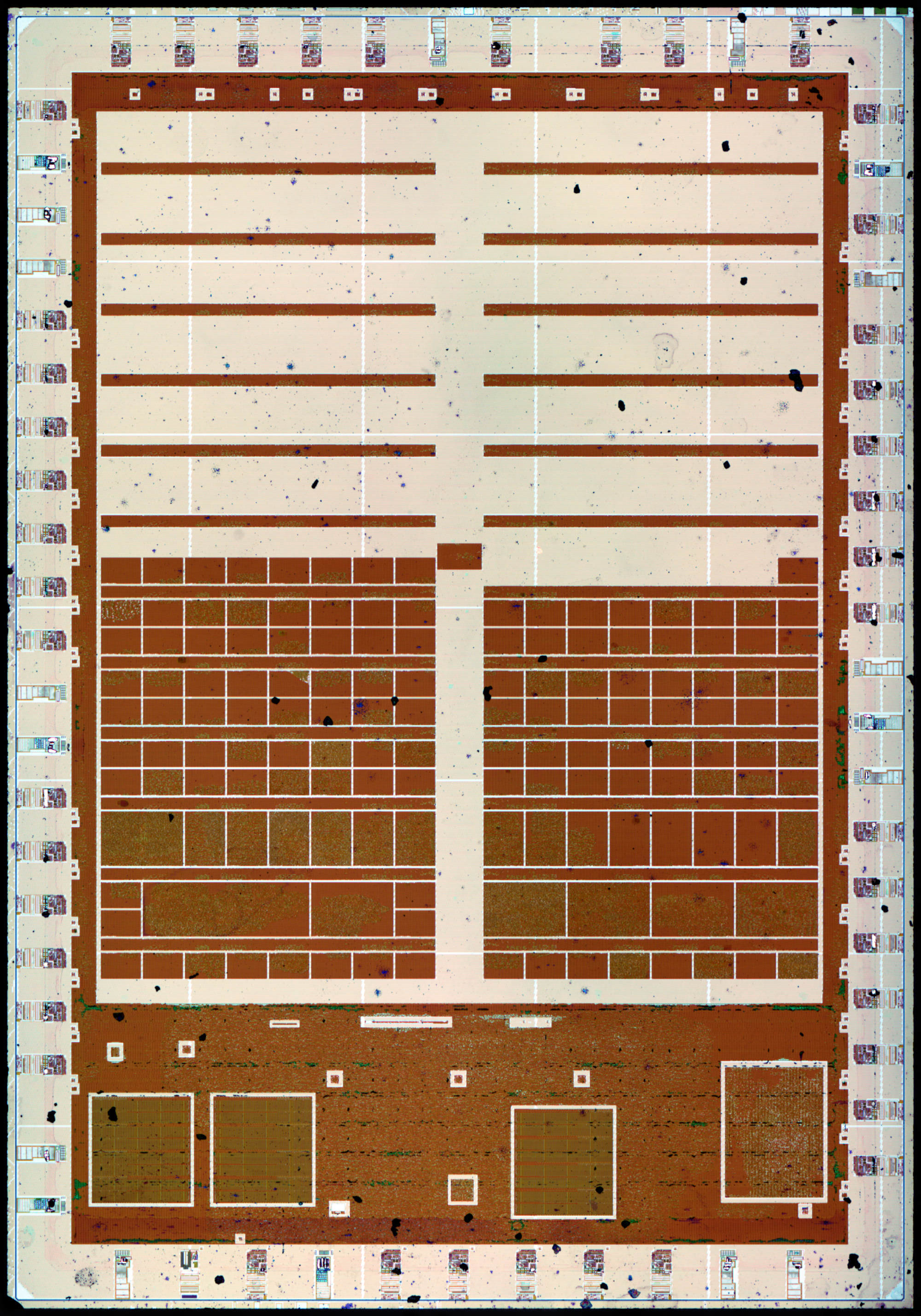

Die size 5256x3662 µm.

TT04 with metal removed, side illumination for looks:

On top metal everything is covered by power distribution and fill, so not much details below are visible:

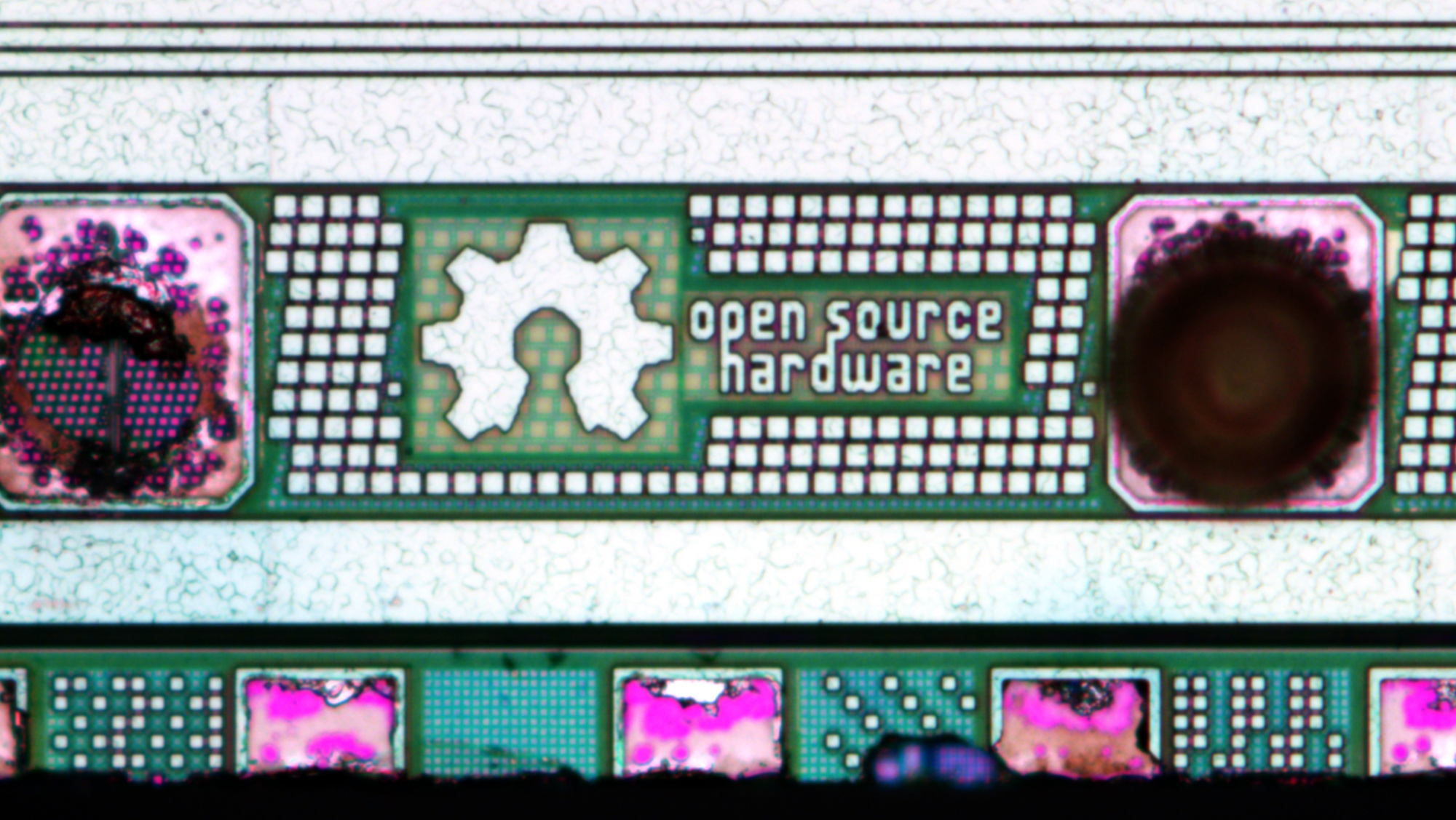

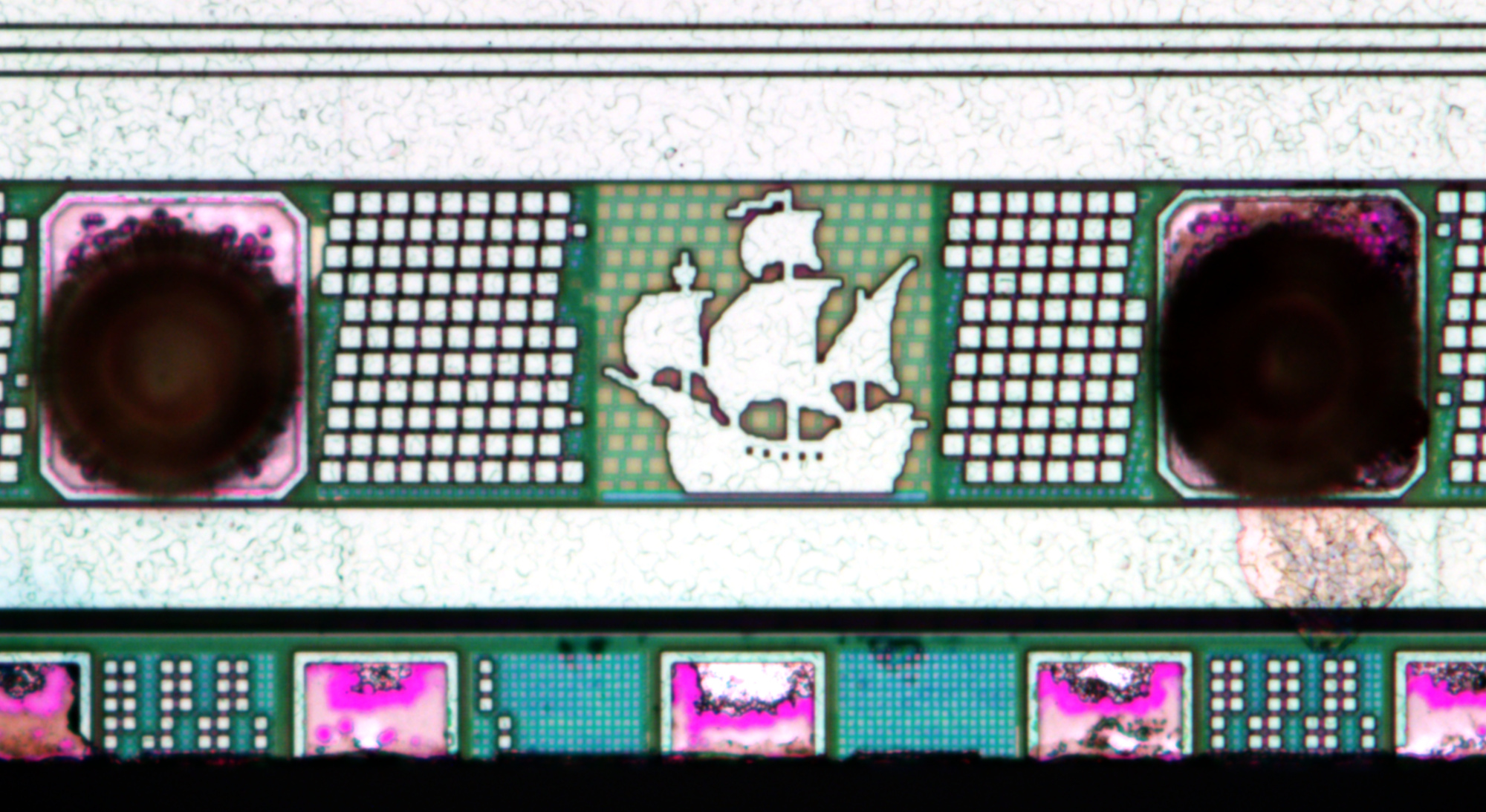

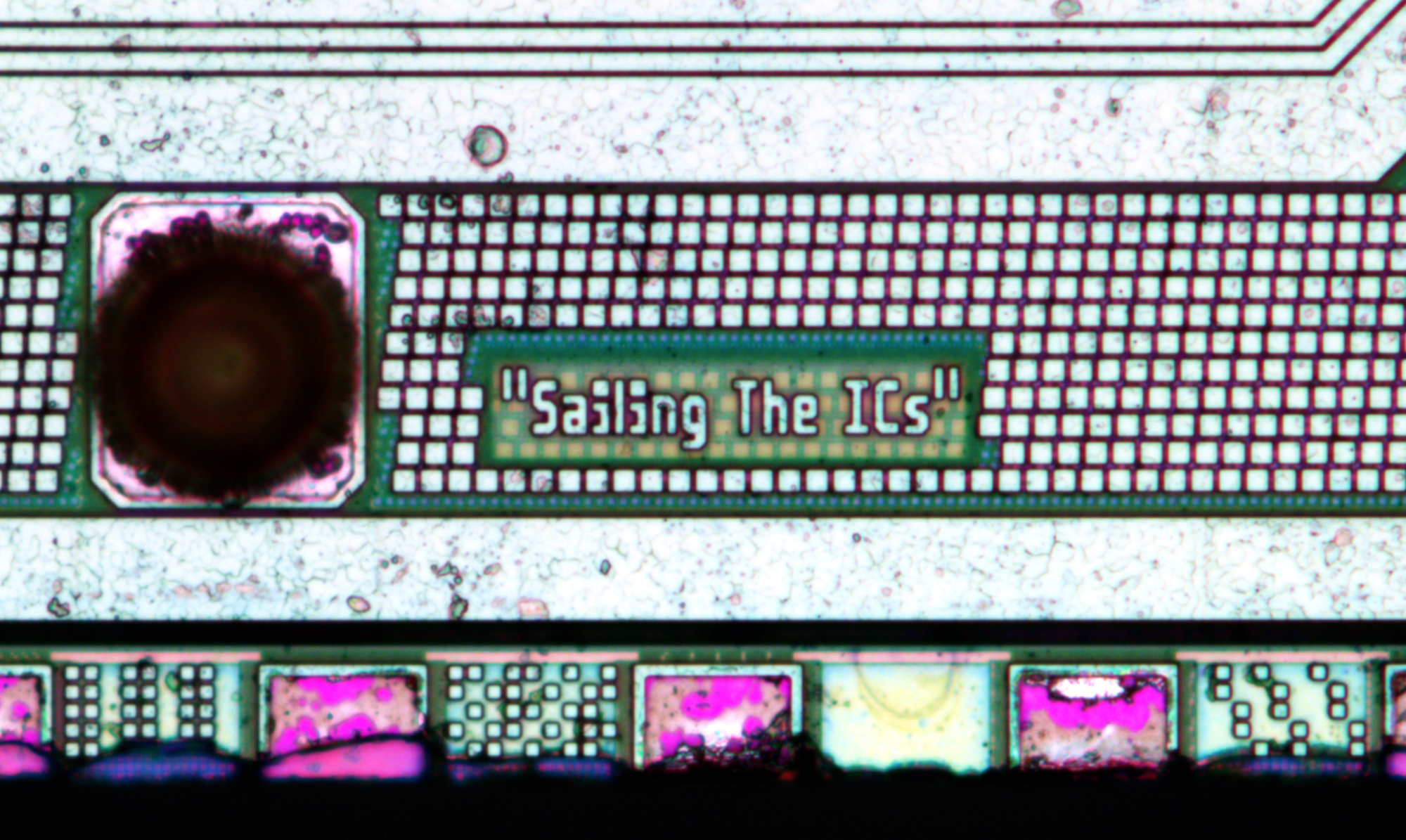

On the right side there are few silicon doodles:

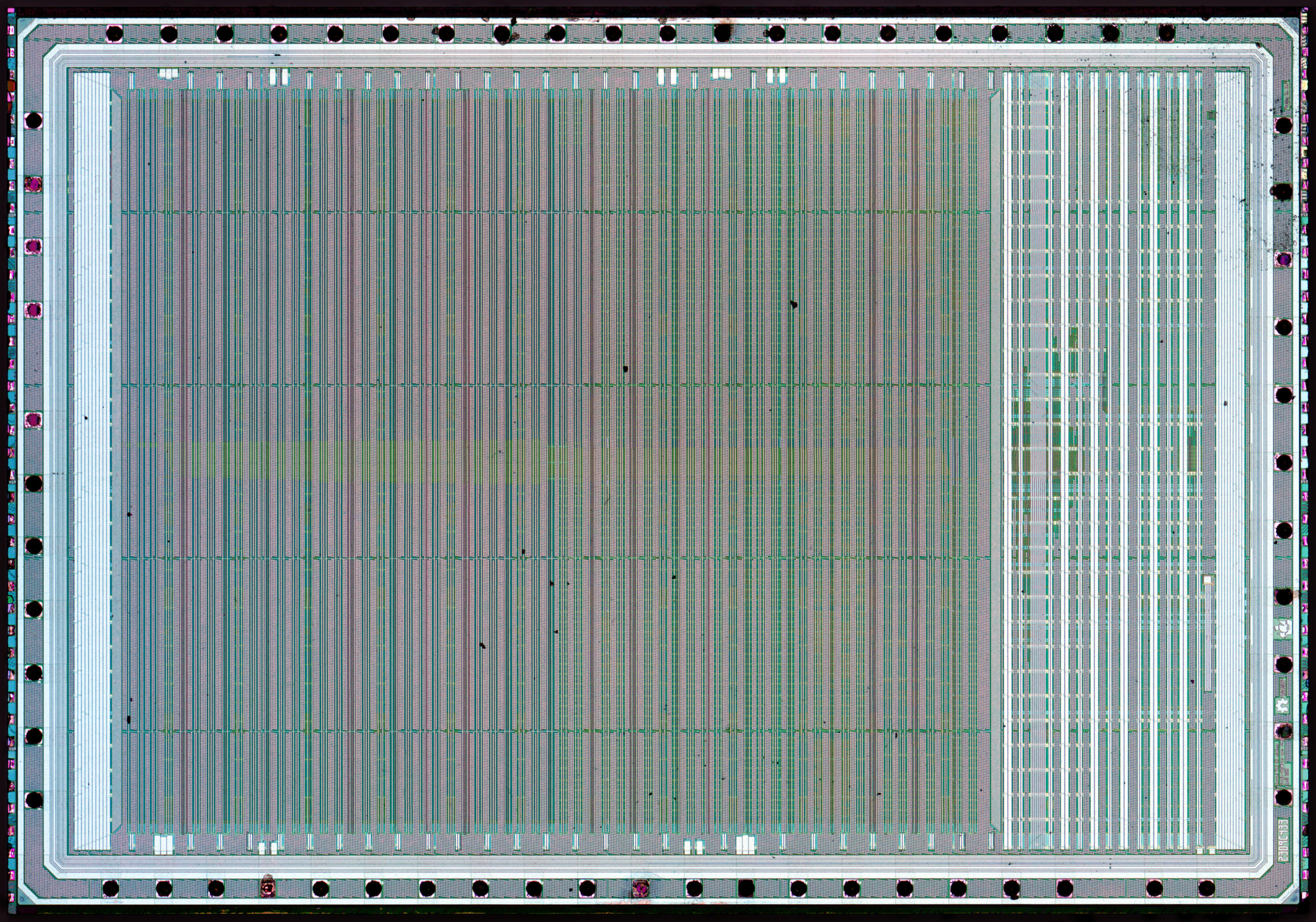

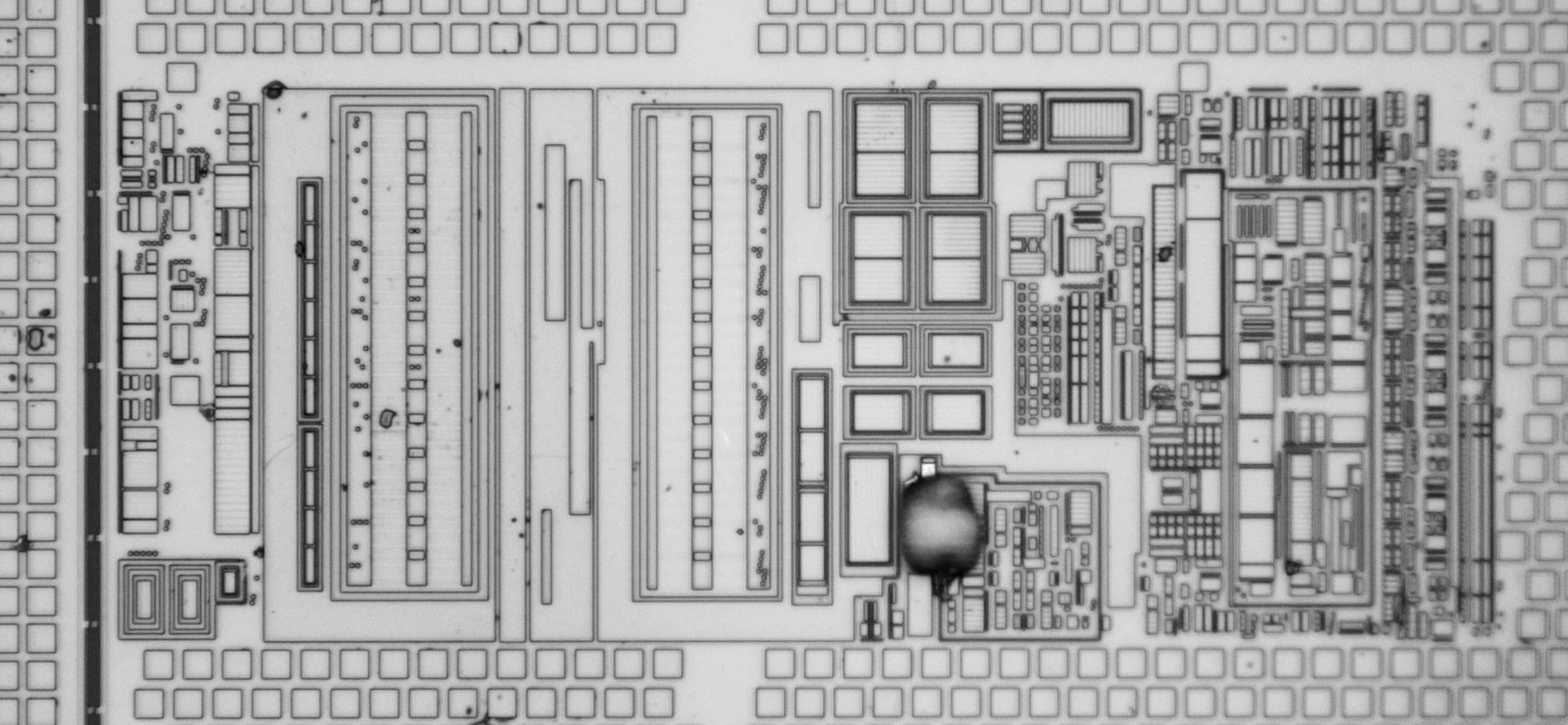

To see under top metal we need to chemically etch glass & metal layers using hydrofluoric acid (HF). Here we can see Caravel management block with RISC-V CPU at the bottom, system controller in the middle and multiple user designs covering lower half of the chip:

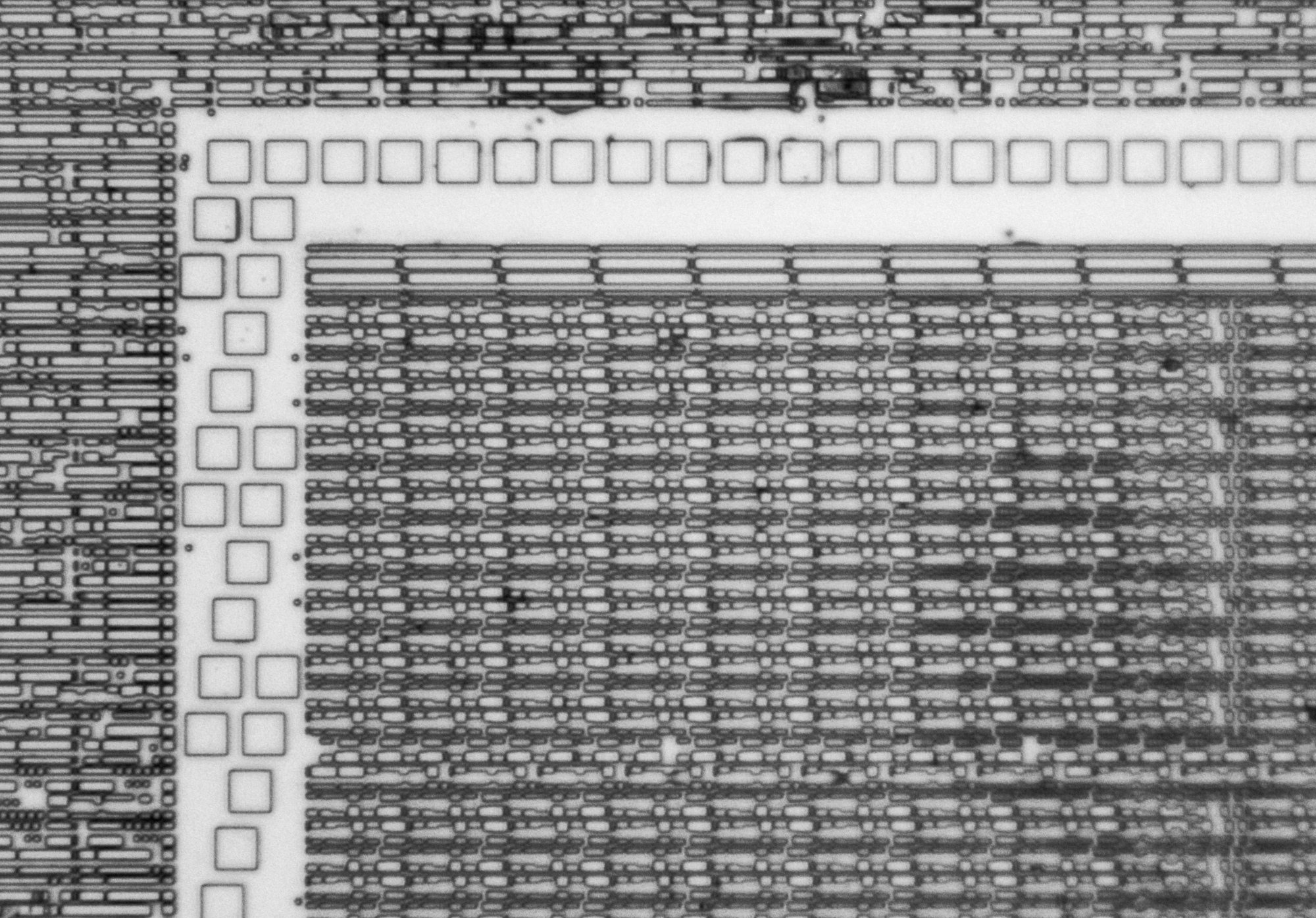

At higher magnification we see that all metals and polysilicon are gone, we likely only see STI (Shallow trench isolation) structures. This is IO cell:

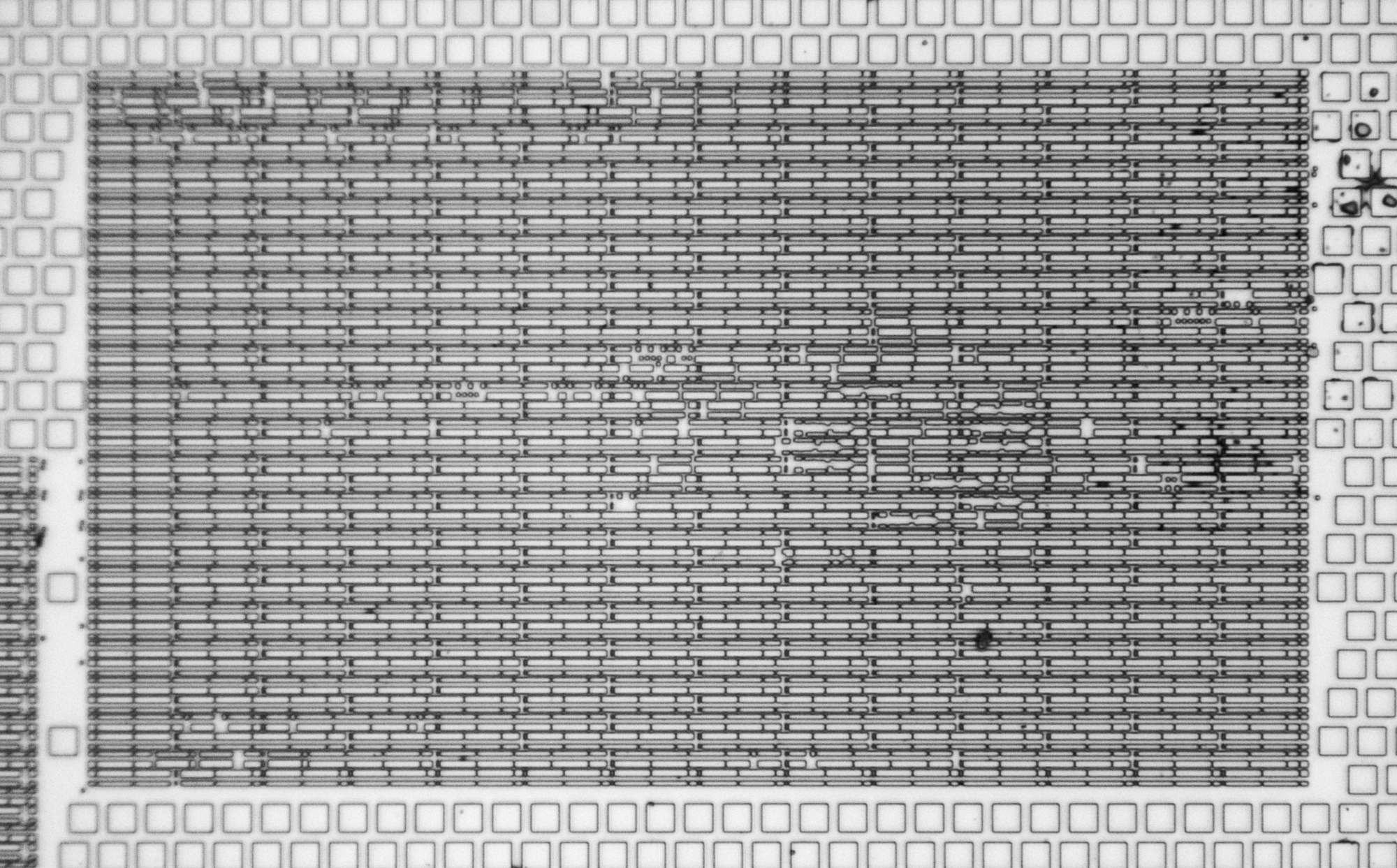

DFF SRAM of the Caravel's RISC-V CPU. DFF memory is used to reduce tapeout risks, but much less area-efficient vs conventional SRAM array:

This is central TinyTapeout controller:

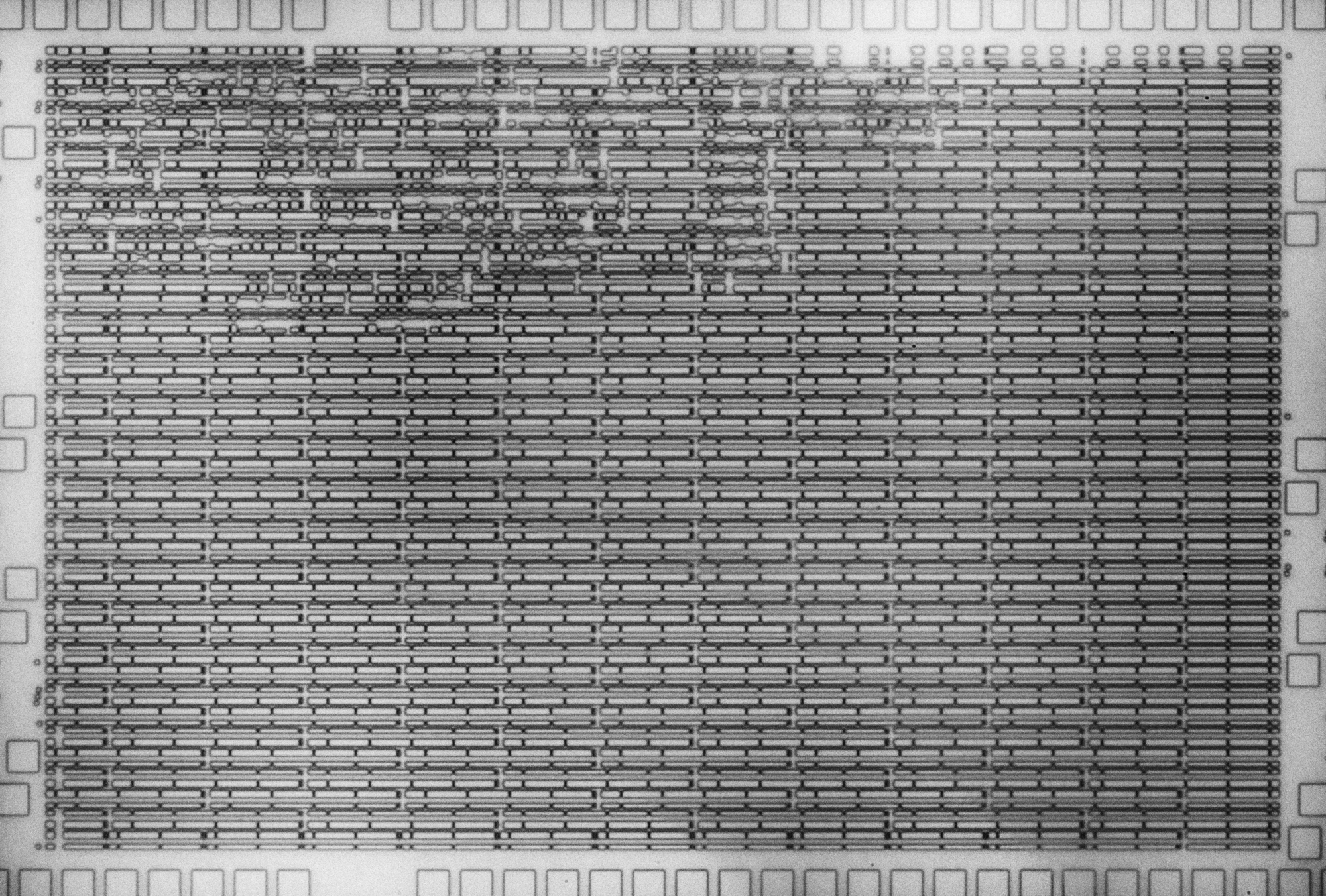

And finally, this is my design:

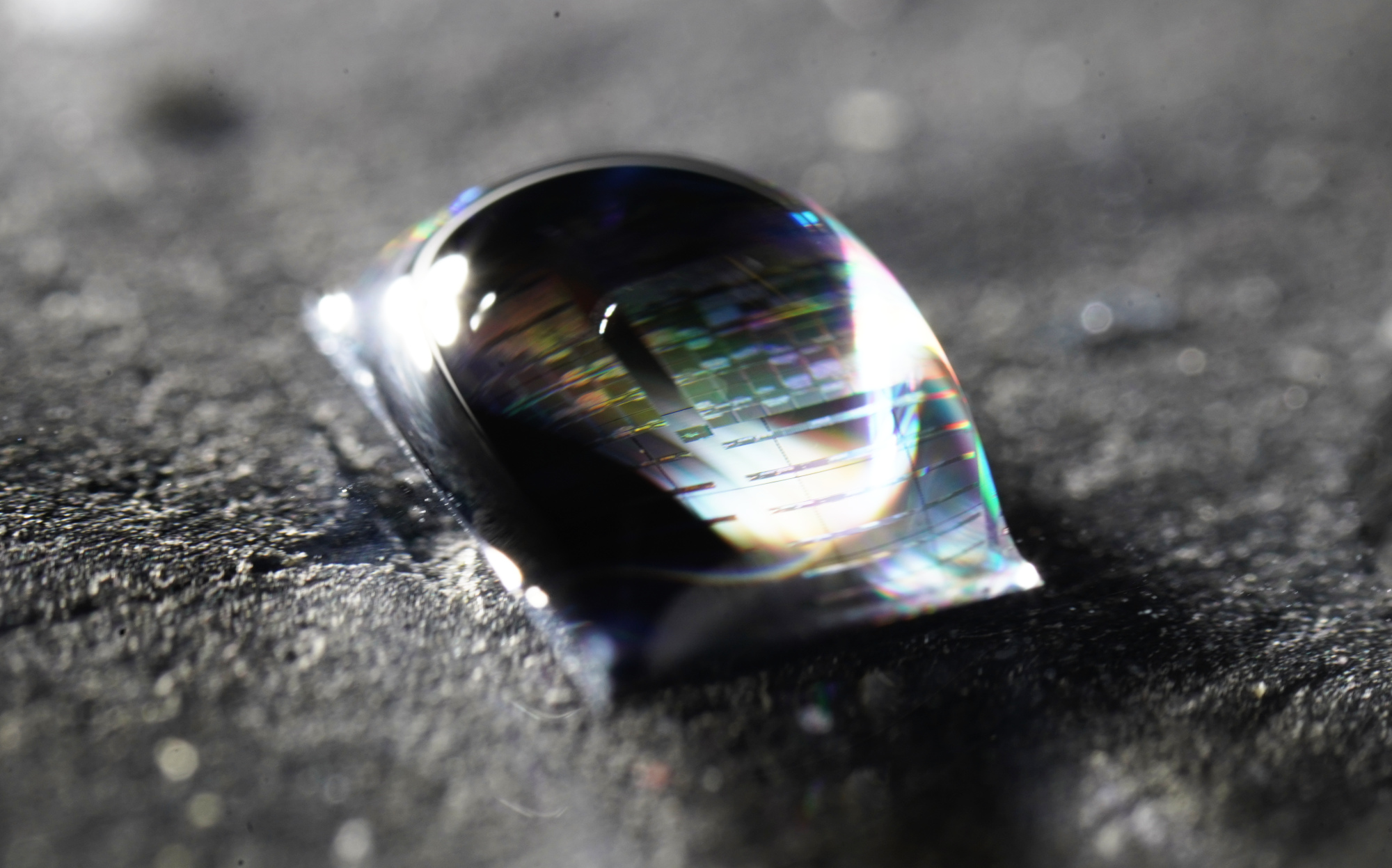

Chip covered by immersion oil during photography: